Dsch 35 Software Free Download

Oct 18, 2017 - Dsch 3.5 Software' title='Dsch 3.5 Software' />Escherichia coli. Crack software download PolyWorks v2015 ASA OILMAP v6. 3 Super HAD CCD Sensor, 35x Optical Zoom 4. Fable 3 Pc Trainer Free Download.

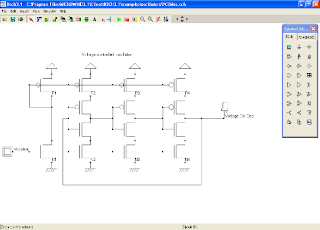

DSCH version 3.5 - Simulate menu Simulate Menu Check Floating Lines The command Insert -> User Symbol is used to add a user defined symbol to the existing schematic diagram. The user symbol is created using the command File -> Schema To new Symbol. The inserted symbol can be fixed at the desired location. Show Critical Path The critical path is the series of logic gates between the output and input with the longest propagation delay.

The command Simulate -> Show Critical Path shows the graph of the critical path. The list of symbols and cumulated delays which build the critical path are also listed. Start Simulation The command ' Start Simulation' launches the electrical net extraction and the logic simulation. The simulation speed may be controlled by the cursor 'Fast-Slow'.

The simulation may be paused, run step by step and stopped. By default, the logic state of all interconnects is made visible. You may also see each pin state by a tic in front of 'Show pin state', or see the details of each symbol using the tic in front of 'Symbol State'. Circuit Testing - Fault simulation () Load or design a schematic diagram including at least one input and one output. Click “Simulate -> Circuit Testing - Fault Simulation'.

The screen shown below appears. The truth-table is displayed for all inputs. In the example below (full-adder loaded from examples/adder/fadd.SCH'), the inputs A,B and C are found in the design. STEP 1 - GET TRUTH TABLE.

Click 'Logic Simulation' and then 'Extract Truth-table' to complete the truth-table. We can see that the outpus 'Carry' and 'Sum' correspond to a full adder. STEP 2 - INJECT FAULT. Click 'Next'. The screen shown below appears.The default type of fault is 'Stuck-at-0', which is applied to inputs A, B and C. Consequently three lines appear: 'A@0' (Input A stuck-at-0), B@0 and C@0. Click 'Generate faults'.

Click 'Simulate Fault 1', then 'Extract fault response'. The first line is filled. Click 'Simulate Fault 2', then 'Extract fault response'. The second line is filled. Click 'Simulate Fault 3', then 'Extract fault response'.

Don't bother with either then.  More of a story and character person? Guilty Crown develops its plot more. Otherwise watch it purely for animation and sound. If you managed to see redeeming qualities in one, you might in another.

More of a story and character person? Guilty Crown develops its plot more. Otherwise watch it purely for animation and sound. If you managed to see redeeming qualities in one, you might in another.

The third line is filled, as displayed below. STEP 3 - ANALYSE VECTORS. The third step consists in selecting the minimum set of test vectors to achieve 100% coverage. In the figure below, the test vectors '011' (A=0, B=1, C=1) and '101' (A=1, B=0, C=1) enable to detect the three potential errors A@0 (A stuck at 0), B@0 and C@0. An application note is proposed that introduces the concept for fault simulation at logic level in Dsch35. The mechanisms for logic fault injection, simulation and optimum test vector extraction are described.

The testing features of Dsch35 are illustrated with a set of logic designs. Click to download the application note. Simulate Options The simulation parameters ( Simulation Options) are: the simulation step (10ps by default), the gate delay, wire delay, supply voltage, and elementary gate current.

This parameters are loaded from.TEC files at initialization or with the command File -> Select Foundry.

Description The DSCH program is a logic editor and simulator. DSCH is used to validate the architecture of the logic circuit before the microelectronics design is started. DSCH provides a user-friendly environment for hierarchical logic design, and fast simulation with delay analysis, which allows the design and validation of complex logic structures. DSCH also features the symbols, models and assembly support for 8051 and PIC16F84 controllers. Designers can create logic circuits for interfacing with these controllers and verify software programs using DSCH. Highlights • User-friendly environment for rapid design of logic circuits. • Supports hierarchical logic design.

• Added a tool on fault analysis at the gate level of digital. Faults: Stuck-at-1, stuck-at-0.

The technique allows injection of single stuck-at fault at the nodes of the circuit. • Improved interface between DSCH and Winspice.

• Handles both conventional pattern-based logic simulation and intuitive on screen mouse-driven simulation. • Built-in extractor which generates a SPICE netlist from the schematic diagram (Compatible with PSPICETM and WinSpiceTM). • Generates a VERILOG description of the schematic for layout conversion. • Immediate access to symbol properties (Delay, fanout). • Model and assembly support for 8051 and PIC 16F84 microcontrollers. • Sub-micron, deep-submicron, nanoscale technology support.

• Supported by huge symbol library.